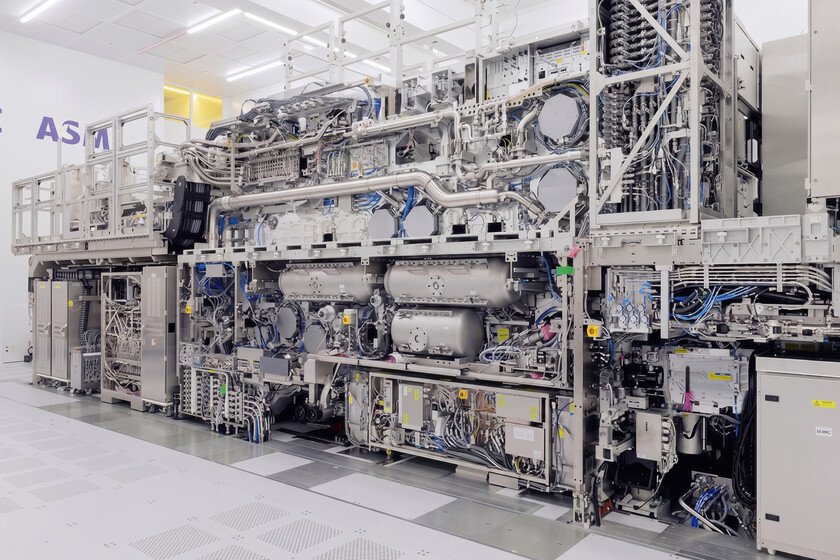

El pasado 23 de abril TSMC oficializó una decisión estratégica muy importante: ha aplazado la adopción de las máquinas de litografía de ultravioleta extremo (UVE) y alta apertura de ASML hasta 2029. Estos son los equipos de fabricación de circuitos integrados más avanzados que tiene actualmente en su porfolio esta compañía de Países Bajos, y el anuncio de TSMC provocó ipso facto una caída del 3,3% del valor de sus acciones. No en vano este productor de chips taiwanés es el mayor cliente de ASML. En 2025 el 23,9% de las ventas totales de esta empresa neerlandesa procedió de TSMC.

El principal motivo por el que esta última compañía ha decidido no usar las máquinas UVE High-NA de ASML a corto plazo es estrictamente económico. Cada una de ellas tiene un precio de unos 350 millones de euros, y, además, una sola planta de semiconductores de vanguardia requiere la instalación de varias decenas de estos equipos. TSMC considera que actualmente son demasiado caras para rentabilizar la fabricación de chips avanzados. Y, curiosamente, Intel, Samsung y SK Hynix ya están adoptando la tecnología High-NA.

Esta decisión de TSMC conlleva grandes desafíos técnicos

El paso que ha dado TSMC no ha sido improvisado, como cabe esperar. De hecho, durante los últimos dos años varios directivos de esta compañía han expresado públicamente sus dudas acerca de la adopción a corto plazo de los equipos High-NA de ASML. En enero de 2024 C.C. Wei, el actual presidente y director general de TSMC, nos sorprendió con esta declaración:

«Estamos estudiándolo minuciosamente, evaluando la madurez de la herramienta y examinando sus costes. Nosotros siempre tomamos la decisión adecuada en el momento oportuno con el propósito de ofrecer el mejor servicio a nuestros clientes», aseguró Wei durante una reunión. Pocas semanas antes Szeho Ng, un analista de China Renaissance, vaticinó que TSMC no utilizaría los equipos UVE de alta apertura de ASML hasta que introdujese su tecnología de integración de 1 nm.

«Nosotros siempre tomamos la decisión adecuada en el momento oportuno con el propósito de ofrecer el mejor servicio a nuestros clientes»

La semana pasada fue Kevin Zhang, el subdirector de operaciones de TSMC, quien aclaró algo muy importante: «Me asombra nuestro equipo de I+D. Sigue encontrando formas de impulsar el desarrollo tecnológico sin usar los equipos UVE High-NA de ASML. Algún día puede que tengamos que utilizarlos, pero en este momento podemos seguir cosechando beneficios de la tecnología UVE actual sin pasar a la High-NA que, como todos sabemos, es extremadamente costosa».

En 2029 TSMC pretende tener preparadas para la producción a gran escala las tecnologías de integración A12 y A13, que no son otra cosa que derivados de su fotolitografía A14. Desde un punto de vista comercial estas serán las primeras tecnologías de 1,2 y 1,3 nm de esta compañía. Utilizarán transistores GAA (Gate-All-Around) de segunda generación y la tecnología NanoFlex Pro. Esta última innovación permitirá a los diseñadores de circuitos integrados usar celdas rápidas para las partes críticas de la GPU que necesitan velocidad, y celdas densas o eficientes para el resto, optimizando así el área del chip hasta el último milímetro.

Lo que todavía no sabemos es qué soluciones técnicas van a implementar los ingenieros de TSMC para hacer posible la fabricación de circuitos integrados de 1,2 y 1,3 nm empleando los equipos UVE de ASML. Solo es una conjetura, pero parece poco probable que vayan a recurrir al multiple patterning debido a que este procedimiento compromete el rendimiento por oblea y el coste de los semiconductores. TSMC perdería competitividad. Un último apunte: el multiple patterning a grandes rasgos consiste en transferir el patrón a la oblea en varias pasadas con el propósito de incrementar la resolución del proceso litográfico.

Imagen | ASML

Más información | Innovation Origins

En Xataka | Bill Gates ha radiografiado Intel. Y su diagnóstico es abrumadoramente certero